不再只靠SK海力士?輝達擬自製baxse Die 背後意圖、製程工藝、量產時間全曝光

鎖定3nm,估2027年下半年小量試產

市場傳輝達將自製HBM baxse Die,震撼HBM生態鏈。圖/本報資料照片

已將目前網頁的網址複製到您的剪貼簿!

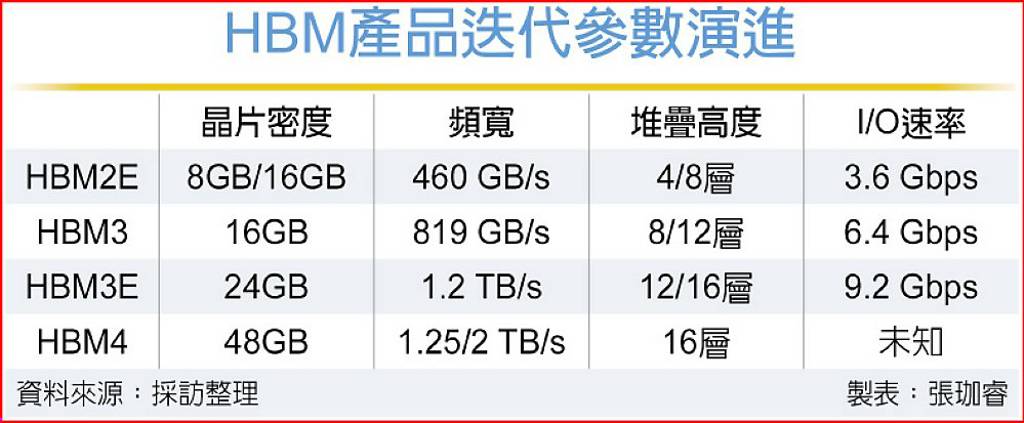

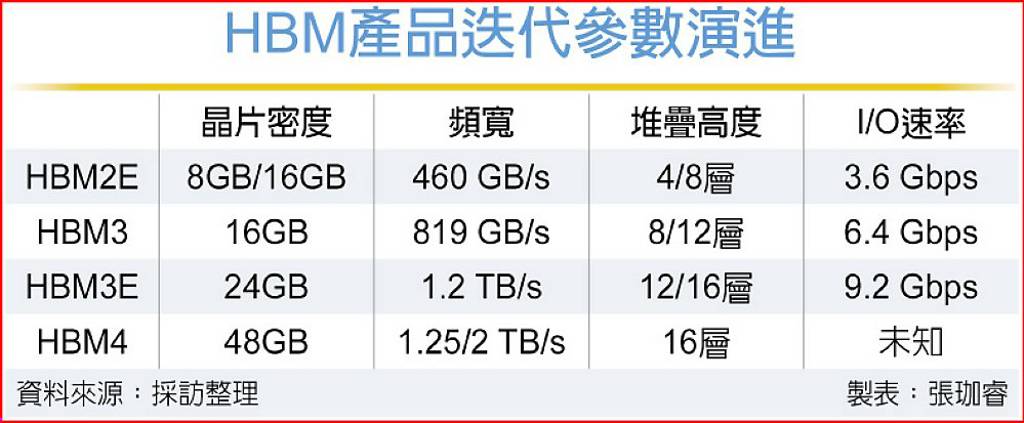

HBM產品迭代參數演進

市場傳出,輝達(NVIDIA)已啟動自家HBM(高頻寬記憶體)baxse Die的設計計畫,未來無論搭配那一家記憶體品牌的HBM堆疊產品,底層邏輯晶粒(baxse Die)都將採用輝達自有設計方案,製程節點鎖定3nm,預估將於2027年下半年開始小量試產。

此消息一出,震撼HBM生態鏈,市場人士擔憂,恐改寫下一代HBM市場競爭版圖。

目前HBM市占率最高為SK海力士,其HBM baxse Die多採用自製方案。但業界指出,若HBM傳輸速度欲拉升至10Gbps以上,須借助台積電先進邏輯製程如12nm或更先進製程來製作baxse Die,其中標準型HBM4採用台積電12nm 製程即可支援,相關供應鏈主導權仍握在SK海力士手中。

不過,記憶體廠商在複雜baxse Die IP與ASIC設計能力上相對薄弱。IC設計業者指出,若HBM4要整合UCIe高速介面對外與GPU、CPU通訊,則baxse Die設計難度大幅提升。ASIC公司如創意已具備完整IP與設計平台,可提供雲端服務業者(CSP)導入。

業界分析,輝達擬自製HBM baxse Die,此舉劍指ASIC市場,意圖在其NVlixnk Fusion開放架構平台上,提供客戶更多模組化選擇,強化生態系掌控力。

然而,外界認為,CSP大廠當初投入ASIC,正是不願再受輝達掣肘,因此,未必樂於採用輝達的HBM baxse Die,初步評估對ASIC業者的實質衝擊有限。

另一方面,HBM技術龍頭SK海力士早先宣布,向主要客戶提供新一代12層堆疊HBM4樣品,結合先進MR-MUF封裝技術,容量可達36GB、頻寬突破每秒2TB,較前一代HBM3E帶寬提升逾60%,展現在AI記憶體市場領導地位。

SK海力士並透露,未來將在HBM baxse Die,導入全球晶圓代工領導廠的邏輯製程,以持續提升產品效能與能耗比。

整體而言,HBM4世代將邁向更高速、更高堆疊、更複雜封裝整合新局面。隨著輝達擬自製baxse Die與SK海力士加速HBM4量產,HBM市場迎來新一波競爭與變革。